June 7, 2018

By: Michael Feldman

This week at the Computex computer tradeshow in Taipei, AMD CEO Lisa Su outlined where her company stood with its next-generation Radeon Instinct GPU and its Zen 2 EPYC CPU.

Although much of AMD’s presentation had to do with its client-side processor business, Su put a lot of emphasis on their upcoming server silicon and specifically took aim at the HPC end of the business. “We are absolutely about high performance computing,” she declared.

Although much of AMD’s presentation had to do with its client-side processor business, Su put a lot of emphasis on their upcoming server silicon and specifically took aim at the HPC end of the business. “We are absolutely about high performance computing,” she declared.

The server chips in question are new versions of the Radeon Instinct GPU and the EPYC CPU. Both will be manufactured with 7nm process technology, which according to AMD, will provide twice the transistor density and energy efficiency as its 14nm parts, while delivering 1.35 the performance. We’re not sure how they came up with that performance figure, given the wide variation in application behavior on a given processor. That aside, the jump from 14nm to 7nm should bump up performance significantly, regardless of any design upgrades.

In the case of the second-generation Radeon Instinct GPU, AMD is sticking with its existing Vega architecture, which was used on the original high-end Instinct part, the MI25. That GPU delivered 24.6 teraflops at half precision (FP16), 12.29 teraflops at single precision, but just 0.768 teraflops at full double precision (FP64). The low amount of 64-bit performance was a consequence of the product line’s intended market, namely AI/machine learning and ray-traced image rendering, where 64-bit math doesn’t make much sense.

Moving this GPU to 7nm could presumably double those peak performance numbers, but we’ll have to wait and see how AMD spreads those smaller transistors around. The new GPU will also come with 32 GB of HBM2, doubling the 16 GB of the MI25, and matching the HBM2 capacity on NVIDIA’s latest V100 GPU and Intel’s upcoming “Lake Crest” Neural Network Processor.

The chip is sampling now to select customers and is scheduled to be generally available later in the year.

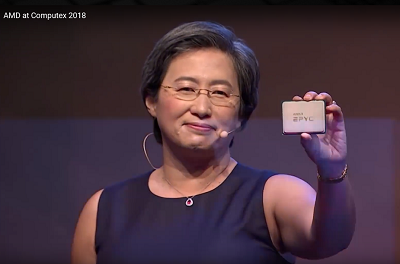

The Zen 2 EPYC processor, code-named “Rome,” is still in the lab, although Su did hold up a sample chip for the crowd. The CEO did not offer much in the way of technical details on the future silicon but did mention that the new processor will fit into the same socket as the first-generation EPYC. The rationale is that they want make sure their current EPYC customers can migrate easily to the second-generation CPUs once they become available. That follows the playbook the company used back in the Opteron days, when AMD kept the socket constant through multiple generations of CPUs.

Although Su did not talk about the architectural changes in Zen 2, at previous venues the company has stated that the future EPYC will support the new PCIe Gen4 bus and xGMI, AMD’s latest Global Memory Interconnect for multi-chip modules. More broadly, AMD has promised the new design will improve on the original Zen in “multiple dimensions.” That suggests things like more cores, faster clock speeds, more instructions per clock cycle, and bigger caches. But again, we’ll have to wait and see.

The Zen 2 EPYC processors are on track to sample in the second half of this year, with a commercial launch sometime in 2019.