Sept. 14, 2017

By: Michael Feldman

Taiwan Semiconductor Manufacturing Company (TSMC) is collaborating with Xilinx, Cadence Design Systems, and ARM to develop a test chip that support the new high performance interconnect standard, known as CCIX.

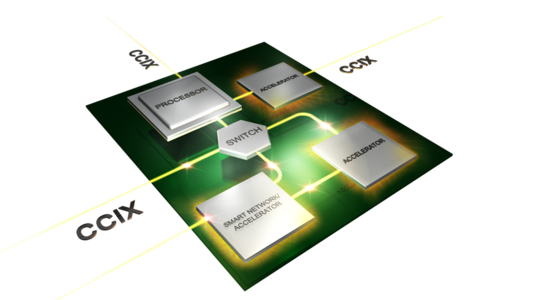

The Cache Coherent Interconnect for Accelerators (CCIX) standard enables processors and coprocessor to access cache and memory with extremely low levels of latency, the idea being to treat CPUs, GPUs, FPGAs, network adapters, and custom ASICs as equal peers with regard to on-board data. The impetus behind CCIX is a new set of datacenter applications, in particular, machine learning, network processing, storage off-load, in-memory data base and 4G/5G wireless technology, which are all demanding heterogeneous hardware. With this new cache-coherent standard, you have an architecture-neutral interconnect that can be broadly adopted by vendors. At least, that’s the idea.

The Cache Coherent Interconnect for Accelerators (CCIX) standard enables processors and coprocessor to access cache and memory with extremely low levels of latency, the idea being to treat CPUs, GPUs, FPGAs, network adapters, and custom ASICs as equal peers with regard to on-board data. The impetus behind CCIX is a new set of datacenter applications, in particular, machine learning, network processing, storage off-load, in-memory data base and 4G/5G wireless technology, which are all demanding heterogeneous hardware. With this new cache-coherent standard, you have an architecture-neutral interconnect that can be broadly adopted by vendors. At least, that’s the idea.

According to the joint press release on the TSMC collaboration, the chip “aims to provide a silicon proof point to demonstrate the capabilities of CCIX in enabling multi-core high-performance ARM CPUs working via a coherent fabric to off-chip FPGA accelerators.” Since no ARM chip vendors were revealed to be part of the collaboration -- ARM itself does not manufacture processors – the test chip will presumably be a reference platform for ARM server chipmakers, like Cavium and Qualcomm, both of which are members of the CCIX consortium.

“With the surge in artificial intelligence and big data, we’re seeing increasing demand for more heterogeneous compute across more applications,” said Noel Hurley, vice president and general manager, Infrastructure Group, ARM. “The test chip will not only demonstrate how the latest ARM technology with coherent multichip accelerators can scale across the data center, but reinforces our commitment to solving the challenge of accessing data quickly and easily. This innovative and collaborative approach to coherent memory is a significant step forward in delivering high-performance, efficient data center platforms.”

Xilinx currently uses TSMC as the manufacturer of its Virtex UltraScale+ FPGAs, which are being targeted to HPC analytics and image recognition, 4K/8K video processing and network function virtualization/bridging. The platform includes the second-generation high bandwidth memory (HBM Gen2), as well as hard IP for the CCIX interface. The test ARM chip produced by the collaboration will provide cache-coherent connectivity to these same Virtex UltraScale+ FPGAs.

The CCIX test chip will be manufactured on TSMC’s 7nm FinFET process technology, and is targeted for tape-out in the first quarter of 2018, with general availability expected in the second half of the year.